Phase Locked Loop Block Diagram

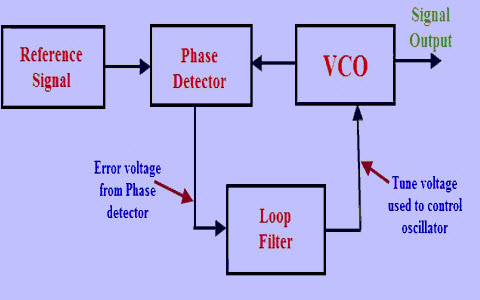

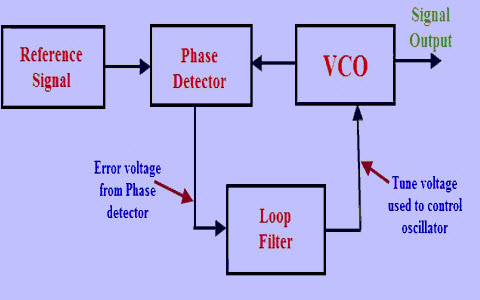

Figure 1 shows a simplified block diagram of the major components in a pll. The phase locked loop or pll is an electronic circuit with a voltage controlled oscillator whose output frequency is continuously adjusted according to the input signals frequency.

Figure 1 From Fixed Reference Frame Phase Locked Loop Frf

Figure 1 From Fixed Reference Frame Phase Locked Loop Frf

The input signal vi with an input frequency fi is conceded by a phase detector.

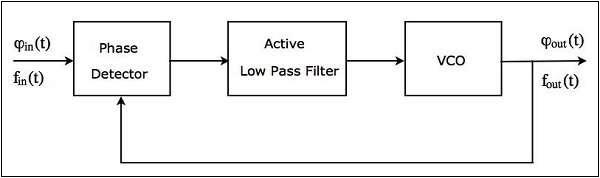

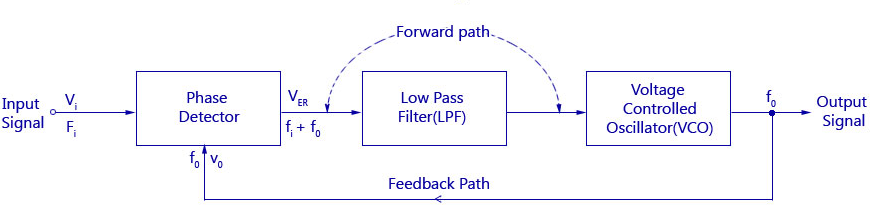

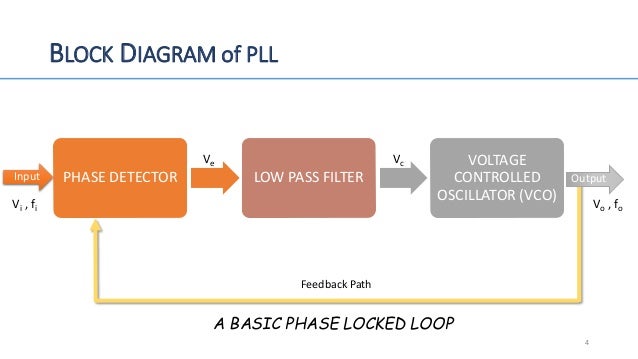

Phase locked loop block diagram. A phase locked loop is used for tracking phase and frequency of the input signal. Block diagram and working principle of pll the phase locked loop consists of a phase detector a voltage control oscillator and in between them a low pass filter is fixed. A phase detector basically a comparator which compares the input frequency fiwith the feedback frequency fo the phase detector provides an output error voltage ver fifowhich is a dc voltage.

What is phase locked loop. Phase locked loops are the circuits used to maintain synchronization between input and output frequency of oscillator circuits by comparing the difference in phase of the two signalswith the evolution of ic it has emerged as the basic building block of electronic circuits. A versatile building block for micropower digital and analog applications 3 cd4046b pll technical description figure 2 shows a block diagram of the cd4046b which has been implemented on a single monolithic integrated circuit.

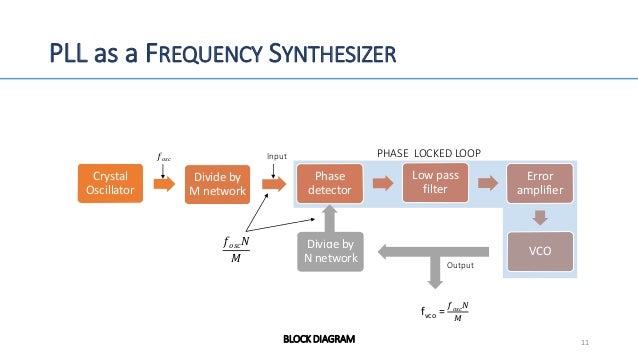

Phase locked loop system block diagram the figure shows the block diagram of the phase locked loop system in fm transmitter that consists of different blocks such as a crystal oscillator phase detector loop filter voltage controlled oscillator vco and frequency divider. The error signal is then low pass filtered and used to drive a vco which creates an output phase. Block diagram phase locked loops the input signal vi with an input frequency fi is passed through a phase detector.

Here the phase of the signals from the vco and the incoming reference signal are compared and a resulting difference or error voltage is produced. Block diagram of a phase locked loop a phase detector compares two input signals and produces an error signal which is proportional to their phase difference. It is a very useful device for synchronous communication.

A phase locked loop pll is a closed loop frequency control system based on the phase difference between the input clock signal and the feedback clock signal of a controlled oscillator. 4 cd4046b phase locked loop. The pll structure consists of a low power linear vco and two.

Phase locked loop diagram showing voltages the voltage controlled oscillator vco within the pll produces a signal which enters the phase detector.

Phase Lock Loop Digital Control And Systems Timothy Walters

Block Diagram Of The Phase Locked Loop Circuit Download

Block Diagram Of The Phase Locked Loop Circuit Download

Phase Locked Loop Ic Tutorialspoint

Phase Locked Loop Ic Tutorialspoint

Phase Locked Loop Block Diagram Download Scientific Diagram

Phase Locked Loop Block Diagram Download Scientific Diagram

File Analog Pll Block Diagram Png Wikimedia Commons

Electronics Phase Locked Loop Pll

Electronics Phase Locked Loop Pll

Phase Locked Loop Design And Construction Elliot Nwaobi

Phase Locked Loop Design And Construction Elliot Nwaobi

Figure 1 From Design Of High Order Phase Lock Loops

Figure 1 From Design Of High Order Phase Lock Loops

Phase Locked Loops In An Ic Based Clock Distribution System

Phase Locked Loops In An Ic Based Clock Distribution System

Phase Locked Loop Operating Principle And Applications

Phase Locked Loop Operating Principle And Applications

The Working Of Phase Detector In Pll Adsantec

The Working Of Phase Detector In Pll Adsantec

Phase Locked Loop Operating Principle And Applications

Phase Locked Loop Operating Principle And Applications

Solved Chapter 4 Problem 37qp Solution Electronic

Solved Chapter 4 Problem 37qp Solution Electronic

Block Diagram Of The Phase Locked Loop Units For A Sub Thz

Block Diagram Of The Phase Locked Loop Units For A Sub Thz

Basic Introduction Of Phase Locked Loop Pll Sharing Is

Basic Introduction Of Phase Locked Loop Pll Sharing Is

3 Phase Locked Loop Block Diagram Download Scientific Diagram

Figure 1 From A 32nm And 0 9v Cmos Phase Locked Loop With

Figure 1 From A 32nm And 0 9v Cmos Phase Locked Loop With

Vhf Community Radio Electronics An Introduction

Vhf Community Radio Electronics An Introduction

Block Diagram Of Phase Locked Loop Download Scientific

Block Diagram Of Phase Locked Loop Download Scientific

Block Diagram Of 565 Pll Wiring Diagram

Simulating Phase Locked Loops With Matlab

Explain Pll Using Block Diagram Of Ic 565

Explain Pll Using Block Diagram Of Ic 565

Principle Block Diagram Of Phase Locked Loop Download

Principle Block Diagram Of Phase Locked Loop Download

0 Response to "Phase Locked Loop Block Diagram"

Post a Comment